- 您現在的位置:買賣IC網 > Datasheet目錄44 > MIC2310-2ZTS TR (Micrel Inc)IC HOT SWAP CTLR 2CHAN 24TSSOP Datasheet資料下載

參數資料

| 型號: | MIC2310-2ZTS TR |

| 廠商: | Micrel Inc |

| 文件頁數: | 4/34頁 |

| 文件大小: | 473K |

| 描述: | IC HOT SWAP CTLR 2CHAN 24TSSOP |

| 標準包裝: | 2,500 |

| 類型: | 熱交換控制器 |

| 應用: | 通用 |

| 內部開關: | 無 |

| 電流限制: | 可調 |

| 電源電壓: | 10.8 V ~ 13.2 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 24-TSSOP(0.173",4.40mm 寬) |

| 供應商設備封裝: | 24-TSSOP |

| 包裝: | 帶卷 (TR) |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

Micrel, Inc.

MIC2310

July 2008

4

M9999-070108-A

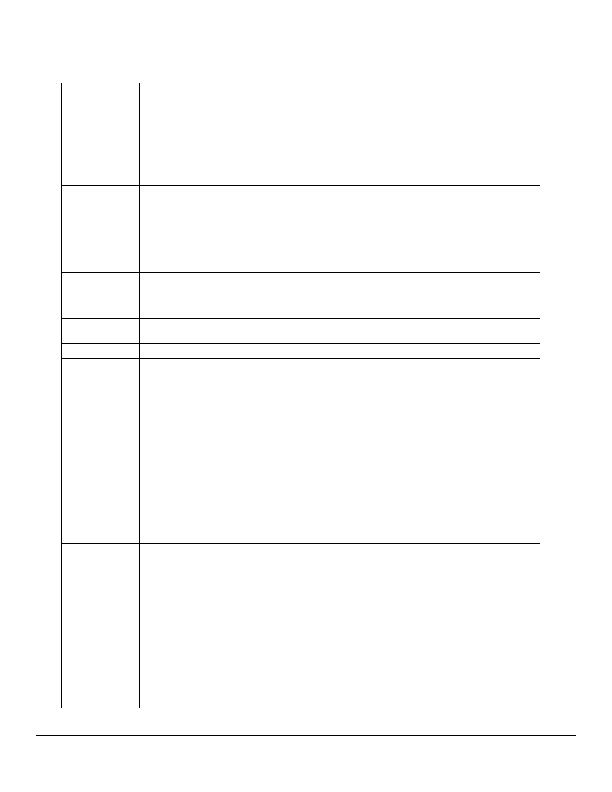

Pin Description

Pin Number

Pin Name

Pin Function

1

UVLO

Undervoltage Lockout Input. When the applied voltage at the UVLO pin is higher

than the controllers V

UVLOH

threshold voltage, the GATE drive circuits are active

when ENABLE= HIGH. If the applied voltage at the UVLO pin falls below the

controllers V

UVLOL

threshold voltage, the GATE drive circuits are disabled to turn

the external MOSFET OFF. In addition, the DISCH circuit is activated to drive an

optional, external discharge transistor alone (illustrated in the Typical Application

circuit) or in combination with an SCR for a very fast discharge circuit

configuration.

2

OVP

Overvoltage Protection Input. When the applied voltage at the OVP pin is higher

than the controllers V

OVPH

threshold voltage, the GATE drive circuit is disabled

to turn the external MOSFET OFF. In addition, the DISCH circuit is activated to

drive an optional, external discharge transistor alone (illustrated in the Typical

Application circuit) or in combination with an SCR for a very fast discharge circuit

configuration. Using an external resistor divider, the UVLO and the OVP pins

form a window comparator that defines the supply voltage range within which the

load may be safely powered.

3

VISS

Steady-state Output Current Monitor. This output signal provides an analog

voltage that is proportional to the steady-state load current. This signal is

provided as an input to the system supervisor/processor to monitor the dc

current/power level of the application circuit.

4

VREG

Internal +5V Regulator Bypass. Connect a 0.1-礔, 16V ceramic capacitor from

this pin to AGND.

5

NC

No connection

6

ENABLE

ENABLE Input. An active asserted-HIGH digital input that controls the operation

of the MIC2310. Activated after the internal POR timer has terminated, a LOW-

to-HIGH transition on this pin commences a start-up sequence if the applied V

CC

is above the V

UVLOH

and below the V

OVPH

threshold voltages. While ENABLE =

LOW, the GATE pin is held to 0V and the DISCH output is activated. The

ENABLE input can be used to reset the internal circuit breaker by applying a

HIGH-to-LOW-to-HIGH transition as defined by t

ENLPW

following either a load

current fault, an open LOADSENSE fault, an open GNDSENSE fault, or a

shorted RSENSE fault.

7

S0

8

S1

Secondary OC Detector Current Threshold Digital Inputs S1 is the MSB and

S0 is the LSB. When used together, S[1:0] sets the overcurrent threshold for the

secondary overcurrent detection circuit to one of four levels relative to the

primary overcurrent detector nominal threshold. For example, S[1:0] = L, L sets

the secondary overcurrent threshold at 1.3X; S[1:0] = L, H sets a 1.5X threshold;

S[1:0] = H, L sets a 2X threshold, and S[1:0] = H, H sets a 1.75X threshold. If the

S[1:0] pins are not connected or left NC, the default setting is S[1:0] = L, L or

1.3X. The permissible voltage range on these inputs is AGND d S[1:0] d V

CC

.

9

CRETRY

Auto-retry Timing Capacitor. A capacitor connected from the CRETRY pin to

AGND configures the MIC2310 to re-start automatically with ENABLE = HIGH

after the circuit breaker trips and latches off. It also sets the

cool-off

time delay

before a new load current start-up sequence is initiated. To configure the

MIC2310s circuit breaker to latch off after fault, connect this pin to AGND. The

circuit breaker latches OFF and remains latched OFF unless the ENABLE input

is toggled HIGH-to-LOW-to-HIGH as defined by t

ENLPW

or the V

CC

supply voltage

is turned OFF then ON.

10

CPRIMARY Primary Overcurrent Detector Timing Capacitor. Connecting a capacitor from the

CPRIMARY pin to AGND sets the response time of the controllers primary

overcurrent detection circuit to GATE OFF in the event of an overcurrent

condition. If the CPRIMARY pin is not connected, the primary overcurrent

detection response time defaults to t

POCSENSE

, typically 250祍 as specified in the

Electrical Characteristics Table. The controller incorporates a patent-pending

built-in test for a faulty CPRIMARY capacitor.

相關PDF資料 |

PDF描述 |

|---|---|

| MIC2341-2YTQ | IC HOT PLUG CTLR DUAL PCI 48TQFP |

| MIC2569YQS TR | IC POWER SWITCH CABLECARD 16QSOP |

| MIC2583R-MBQS TR | IC CTRLR HOT SWAP 200MV 16-QSOP |

| MIC2585-2MBTS TR | IC CTRLR HOT SWAP DUAL 24-TSSOP |

| MIC2586R-2BM TR | IC CTRLR/SEQ HOT SWAP 14-SOIC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MIC23150-4YMT EV | 功能描述:電源管理IC開發工具 2.0A 4MHz HyperLight Load Buck Regulator - Evaluation Board RoHS:否 制造商:Maxim Integrated 產品:Evaluation Kits 類型:Battery Management 工具用于評估:MAX17710GB 輸入電壓: 輸出電壓:1.8 V |

| MIC23150-4YMT TR | 功能描述:直流/直流開關調節器 2.0A 4MHz HyperLight Load Buck Regulator RoHS:否 制造商:International Rectifier 最大輸入電壓:21 V 開關頻率:1.5 MHz 輸出電壓:0.5 V to 0.86 V 輸出電流:4 A 輸出端數量: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:PQFN 4 x 5 |

| MIC23150-4YMT-TR | 功能描述:Buck Switching Regulator IC Positive Fixed 1.2V 1 Output 2A 8-VFDFN Exposed Pad, 8-MLF? 制造商:microchip technology 系列:HyperLight Load? 包裝:剪切帶(CT) 零件狀態:有效 功能:降壓 輸出配置:正 拓撲:降壓 輸出類型:固定 輸出數:1 電壓 - 輸入(最小值):2.7V 電壓 - 輸入(最大值):5.5V 電壓 - 輸出(最小值/固定):1.2V 電壓 - 輸出(最大值):- 電流 - 輸出:2A 頻率 - 開關:4MHz 同步整流器:是 工作溫度:-40°C ~ 125°C (TJ) 安裝類型:表面貼裝 封裝/外殼:8-VFDFN 裸露焊盤,8-MLF? 供應商器件封裝:8-MLF?(2x2) 標準包裝:1 |

| MIC23150-55YMT TR | 功能描述:直流/直流開關調節器 2.0A 4MHz HyperLight Load Buck Regulator RoHS:否 制造商:International Rectifier 最大輸入電壓:21 V 開關頻率:1.5 MHz 輸出電壓:0.5 V to 0.86 V 輸出電流:4 A 輸出端數量: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:PQFN 4 x 5 |

| MIC23150-55YMT-TR | 功能描述:Buck Switching Regulator IC Positive Fixed 1.35V 1 Output 2A 8-UFDFN 制造商:microchip technology 系列:HyperLight Load? 包裝:剪切帶(CT) 零件狀態:停產 功能:降壓 輸出配置:正 拓撲:降壓 輸出類型:固定 輸出數:1 電壓 - 輸入(最小值):2.7V 電壓 - 輸入(最大值):5.5V 電壓 - 輸出(最小值/固定):1.35V 電壓 - 輸出(最大值):- 電流 - 輸出:2A 頻率 - 開關:4MHz 同步整流器:是 工作溫度:-40°C ~ 125°C (TJ) 安裝類型:表面貼裝 封裝/外殼:8-UFDFN 供應商器件封裝:8-TDFN(2x2) 標準包裝:1 |

發布緊急采購,3分鐘左右您將得到回復。