- 您現在的位置:買賣IC網 > PDF目錄114967 > 552AA000107BG (SILICON LABORATORIES) VCXO, CLOCK, 669.32658 MHz, LVPECL OUTPUT PDF資料下載

參數資料

| 型號: | 552AA000107BG |

| 廠商: | SILICON LABORATORIES |

| 元件分類: | VCXO, clock |

| 英文描述: | VCXO, CLOCK, 669.32658 MHz, LVPECL OUTPUT |

| 封裝: | ROHS COMPLIANT, SMD, 6 PIN |

| 文件頁數: | 67/80頁 |

| 文件大小: | 3734K |

| 代理商: | 552AA000107BG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當前第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Si552

Rev. 0.5

7

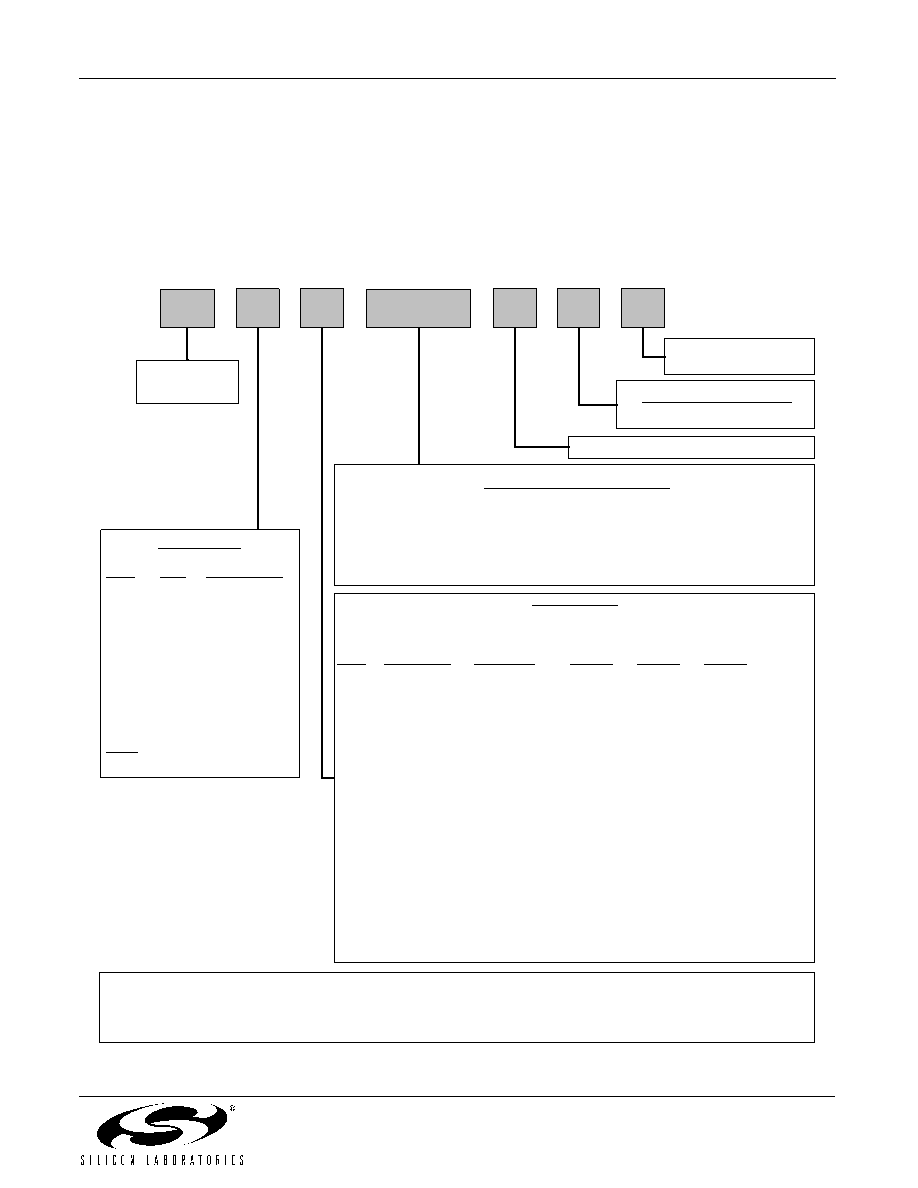

3. Ordering Information

The Si552 was designed to support a variety of options including frequency, temperature stability, tuning slope,

output format, and VDD.

Specific device configurations are programmed into the Si552 at time of shipment.

Configurations are specified using the Part Number Configuration chart shown below. Silicon Labs provides a web

browser-based

part

number

configuration

utility

to

simplify

this

process.

Refer

to

www.silabs.com/VCXOPartNumber to access this tool and for further ordering instructions. The Si552 VCXO

series is supplied in an industry-standard, RoHS compliant, lead-free, 6-pad, 5 x 7 mm package. Tape and reel

packaging is an ordering option.

Figure 1. Part Number Convention

Example Part Number: 552AF000108BGR is a 5 x 7 mm Dual VCXO in a 6 pad package. Since the six digit code (000108) is >

000100, f0 is 644.53125 MHz (lower frequency) and f1 is 693.48299 (higher frequency), with a 3.3 V supply and LVPECL output.

Temperature stability is specified as ±50 ppm and the tuning slope is 135 ppm/V. The part is specified for a –40 to +85 C° ambient

temperature range operation and is shipped in tape and reel format.

DD

R = Tape & Reel

Blank = Trays

Operating Temp Range (°C)

G

–40 to +85 °C

Device Revision Letter

2nd Option Code

Temperature

Tuning Slope

Minimum APR

Stability

Kv

(±ppm)

Code

± ppm (max)

ppm/V (typ)

@ 3.3 V

@ 2.5 V

@ 1.8 V

A

100

180

100

75

25

B

100

90

30

Note 6

C

50

180

150

125

75

D

509080

30

25

E

20

45

25

Note 6

F

50

135

100

75

50

Notes:

1. For best jitter and phase noise performance, always choose the smallest Kv that meets

the application’s minimum APR requirements. Unlike SAW-based solutions which

require higher higher Kv values to account for their higher temperature dependence,

the Si55x series provides lower Kv options to minimize noise coupling and jitter in real-

world PLL designs. See AN255 and AN266 for more information.

2. APR is the ability of a VCXO to track a signal over the product lifetime. A VCXO with an

APR of ±25 ppm is able to lock to a clock with a ±25 ppm stability, over 15 years.

3. Nominal Pull range (±) = 0.5 x VDD x tuning slope.

4. Nominal Absolute Pull Range (±APR) = Pull range – stability – lifetime aging

=0.5 x VDD x tuning slope – stability – 10 ppm

5. Minimum APR values noted above include worst case values for all parameters.

6. Combination not available.

552 Dual VCXO

Product Family

1st Option Code

Code

VDD

Output Format

A

3.3

LVPECL

B3.3

LVDS

C3.3

CMOS

D3.3

CML

E

2.5

LVPECL

F2.5

LVDS

G2.5

CMOS

H2.5

CML

J1.8

CMOS

K1.8

CML

Notes:

CMOS available to 160 MHz.

6-digit Frequency Designator Code

Two unique frequencies can be specified within the following bands of frequencies: 10 to

945 MHz, 970 to 1134 MHz, and 1213 to 1417 MHz. A six digit code will be assigned for

the specified combination of frequencies. Codes > 000100 refer to dual XOs programmed

with the lower frequency value selected when FS = 0, and the higher value when FS = 1.

Six digit codes < 000100 refer to dual XOs programmed with the higher frequency value

selected when FS = 0, and the lower value when FS = 1.

552

X

XXXXXX

B

G

R

相關PDF資料 |

PDF描述 |

|---|---|

| 550AF1060M00BGR | VCXO, CLOCK, 1060 MHz, LVPECL OUTPUT |

| 550CD35M3280BG | VCXO, CLOCK, 35.328 MHz, CMOS OUTPUT |

| 550CE10M0000BG | VCXO, CLOCK, 10 MHz, CMOS OUTPUT |

| 550CC64M0000BGR | VCXO, CLOCK, 64 MHz, CMOS OUTPUT |

| 5G64A-150T-FREQ | VCXO, CLOCK, 1 MHz - 50 MHz, HCMOS/TTL OUTPUT |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 552AA000107DG | 制造商:Silicon Laboratories Inc 功能描述: |

| 552AA000107DGR | 制造商:Silicon Laboratories Inc 功能描述:CNTRLD OSC 622.08MHZ/669.32658MHZ VCXO LVPECL 6PIN - Tape and Reel |

| 552AA000177DG | 制造商:Silicon Laboratories Inc 功能描述: |

| 552AA000177DGR | 制造商:Silicon Laboratories Inc 功能描述: |

| 552AA000240DG | 制造商:Silicon Laboratories Inc 功能描述:CNTRLD OSC 669.32658MHZ/690.75059MHZ VCXO LVPECL 6PIN - Trays |

發布緊急采購,3分鐘左右您將得到回復。